## **Bi-directional 5V Low Capacitance ESD Protector**

### **Description**

The PESDRC2FD5VBL protects sensitive semiconductor components from damage or upset due to electrostatic discharge (ESD) and other voltage induced transient events. They feature large cross-sectional area junctions for conducting high transient currents, offer desirable electrical characteristics for board level protection, such as fast response time, low operating voltage. It gives designer the flexibility to protect one bi-directional line in applications where arrays are not practical.

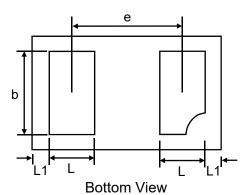

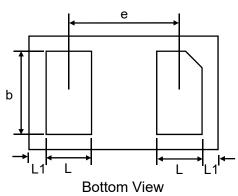

DFN1006-2L(Bottom View)

#### **Feature**

- $\triangleright$  35W peak pulse power per line ( $t_p = 8/20\mu s$ )

- ➤ Ultra-low capacitance: Cj = 0.3pF typ.

- Low clamping voltage

- ➤ DFN1006-2L package

- > Response time is typically < 1 ns

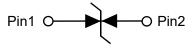

- > Bidirectional configurations

- ➤ RoHS compliant

- ➤ Transient protection for data lines to IEC 61000-4-2(ESD) ±15kV(air), ± 12kV(contact); IEC 61000-4-5 (Lightning) 5.5A (8/20us)

**Circuit Diagram**

Marking (Top View)

### **Applications**

- Cellular phones

- > Portable devices

- Digital cameras

- Power supplies

- ➤ USB 2.0 and USB 3.0

- ➤ HDMI 1.3 and HDMI 1.4

### **Mechanical Characteristics**

- Mounting position: Any

- Qualified max reflow temperature:260°C

- > Device meets MSL 1 requirements

- ➤ DFN1006-2L without plating

### **Electronics Parameter**

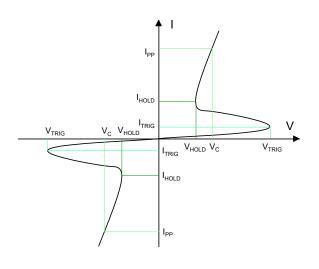

| Symbol            | Parameter                                  |  |  |

|-------------------|--------------------------------------------|--|--|

| $V_{RWM}$         | Peak Reverse Working Voltage               |  |  |

| I <sub>R</sub>    | Reverse Leakage Current @ V <sub>RWM</sub> |  |  |

| $V_{BR}$          | Breakdown Voltage @ I <sub>T</sub>         |  |  |

| I <sub>T</sub>    | Test Current                               |  |  |

| I <sub>PP</sub>   | Maximum Reverse Peak Pulse Current         |  |  |

| V <sub>C</sub>    | Clamping Voltage @ I <sub>PP</sub>         |  |  |

| I <sub>TRIG</sub> | Reverse Trigger Current                    |  |  |

| $V_{TRIG}$        | Reverse Trigger Voltage                    |  |  |

| I <sub>HOLD</sub> | Reverse Holding Current                    |  |  |

| V <sub>HOLD</sub> | Reverse Holding Voltage                    |  |  |

## Electrical characteristics per line@25°C (unless otherwise specified)

| Parameter                      | Symbol         | Conditions                          | Min. | Тур. | Max. | Units |

|--------------------------------|----------------|-------------------------------------|------|------|------|-------|

| Peak Reverse Working Voltage   | $V_{RWM}$      | -                                   | -    | -    | 5    | V     |

| Breakdown Voltage              | $V_{BR}$       | I <sub>t</sub> = 1mA                | 5.6  | -    | 9.0  | V     |

| Reverse Leakage Current        | I <sub>R</sub> | V <sub>RWM</sub> = 5V               | -    | -    | 1.0  | μA    |

| Clamping Voltage <sup>1)</sup> | V <sub>C</sub> | TLP = 16A, $t_p = 100 \text{ns}$    | -    | 13   | -    | V     |

| Clamping Voltage <sup>2)</sup> | V <sub>C</sub> | $I_{PP} = 5.5A, t_{P} = 8/20 \mu s$ | -    | 6.5  | 8.0  | V     |

| Junction Capacitance           | CJ             | $V_R = 0V, f = 1MHz$                | -    | 0.3  | 0.4  | pF    |

## Absolute maximum rating@25°C

| Rating                                         | Symbol           | Value        | Units |

|------------------------------------------------|------------------|--------------|-------|

| Peak Pulse Power ( t <sub>P</sub> = 8/20µs )   | P <sub>PP</sub>  | 35           | W     |

| Peak Pulse Current ( t <sub>P</sub> = 8/20μs ) | I <sub>PP</sub>  | 5.5          | А     |

| Lead Soldering Temperature                     | T <sub>L</sub>   | 260 (10 sec) | °C    |

| Junction and Storage Temperature Range         | $T_{J,}T_{STG}$  | -55~+150     | ℃     |

| ESD Protection-Contact Discharge               | V <sub>ESD</sub> | ±12          | kV    |

| ESD Protection-Air Discharge                   | V <sub>ESD</sub> | ±15          | kV    |

<sup>1.</sup>TLP parameter:  $Z_0$ =50 $\Omega$ ,  $t_p$ =100ns,  $t_r$ =2ns, averaging window from 70ns to 90ns.  $R_{DYN}$  is calculated from 4A to 16A. 2.Non-repetitive current pulse, according to IEC61000-4-5.

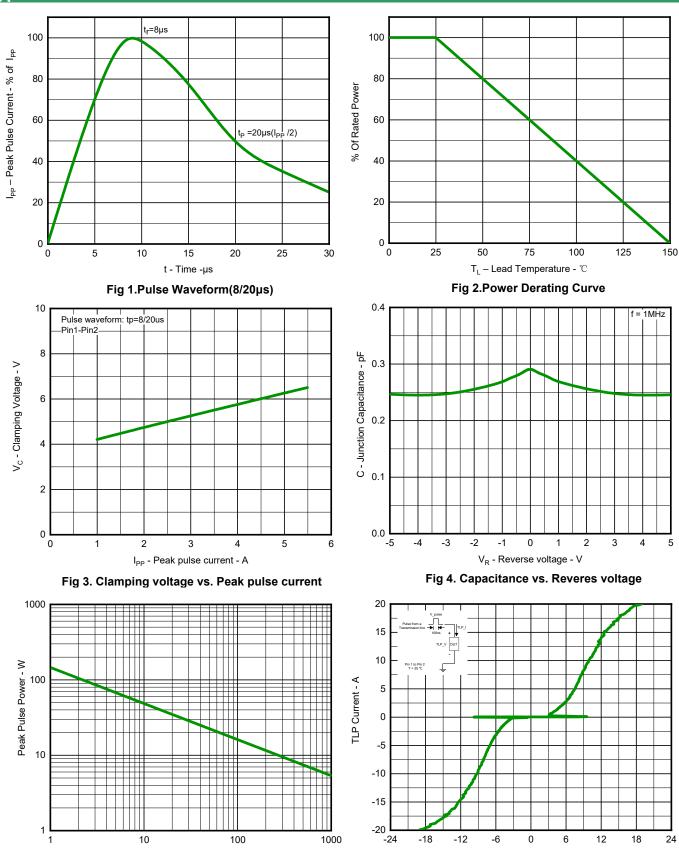

# Typical Characteristics

$\label{eq:pulse Duration - } \mu s$  Fig 5. Non Repetitive Peak Pulse Power vs. Pulse time

TLP Voltage - V Fig 6. TLP Measurement

ESD Protector PESDRC2FD5VBL

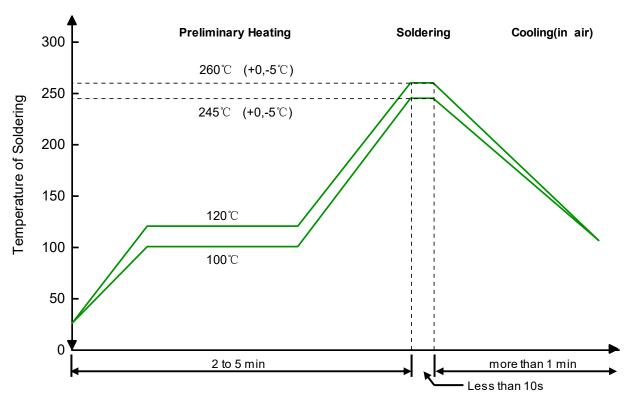

## **Solder Reflow Recommendation**

Remark: Pb free for 260°C; Pb for 245°C.

### **PCB Design**

For TVS diodes a low-ohmic and low-inductive path to chassis earth is absolutely mandatory in order to achieve good ESD protection. Novices in the area of ESD protection should take following suggestions to heart:

- > Do not use stubs, but place the cathode of the TVS diode directly on the signal trace.

- > Do not make false economies and save copper for the ground connection.

- > Place via holes to ground as close as possible to the anode of the TVS diode.

- Use as many via holes as possible for the ground connection.

- Keep the length of via holes in mind! The longer the more inductance they will have.

### **Ordering information**

| Device        | Package                            | Reel | Shipping            |  |

|---------------|------------------------------------|------|---------------------|--|

| PESDRC2FD5VBL | PESDRC2FD5VBL DFN1006-2L (Pb-Free) |      | 10000 / Tape & Reel |  |

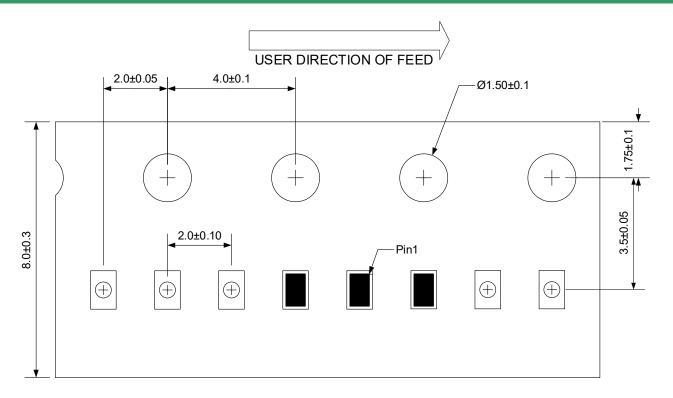

## Load with information

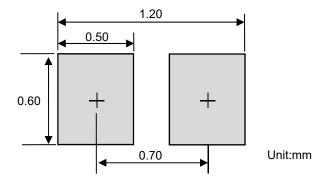

Unit:mm

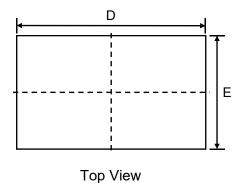

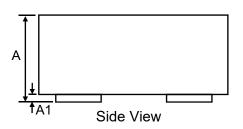

# **Product Dimension (DFN1006-2L)**

| Dim | Millim    | neters | Inches     |       |  |

|-----|-----------|--------|------------|-------|--|

|     | Min       | Max    | Min        | Max   |  |

| Α   | 0.44      | 0.55   | 0.017      | 0.020 |  |

| A1  | 0.00      | 0.05   | 0.000      | 0.002 |  |

| D   | 0.95      | 1.08   | 0.037      | 0.043 |  |

| E   | 0.55      | 0.68   | 0.022      | 0.027 |  |

| b   | 0.40      | 0.60   | 0.016      | 0.024 |  |

| е   | 0.65 Typ. |        | 0.026 Typ. |       |  |

| L   | 0.20      | 0.30   | 0.008      | 0.012 |  |

| L1  | 0.05 Ref. |        | 0.002 Typ. |       |  |

Suggested PCB Layout

#### IMPORTANT NOTICE

🕜 and Prisemi are registered trademarks of Prisemi Electronics Co., Ltd (Prisemi), Prisemi reserves the right to make changes without further notice to any products herein. Prisemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Prisemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in Prisemi data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Prisemi does not convey any license under its patent rights nor the rights of others. The products listed in this document are designed to be used with ordinary electronic equipment or devices, Should you intend to use these products with equipment or devices which require an extremely high level of reliability and the malfunction of with would directly endanger human life (such as medical instruments, aerospace machinery, nuclear-reactor controllers, fuel controllers and other safety devices), please be sure to consult with our sales representative in advance.

Website: http://www.prisemi.com

For additional information, please contact your local Sales Representative.

©Copyright 2009, Prisemi Electronics

Prisemi is a registered trademark of Prisemi Electronics.

All rights are reserved.